一个组合逻辑电路性能优化的目标是使得输入到输出的每条路径的延时都最短。

(2)判断题通过复制电路的方式把关键路径上的分支结构去掉是一种能够缩短关键路径延时的优化技术。

(3)单选题一条组合逻辑路径,调整各级门的尺寸系数使得路径延时最短时对应的条件是

A 所有逻辑门的尺寸系数取最小值

B 所有逻辑门的尺寸系数取面积允许的最大值

C 每级门的门努力都相等

D 门级门的逻辑努力都相等

(4)单选题对于存在多管堆叠结构的大扇入逻辑门,应该把关键输入信号(最晚到达的信号)连接到()

A 内侧的晶体管上

B 外侧的晶体管上

C 尺寸最大的晶体管上

(5)单选题组合逻辑路径存在分支时会使得路径的延时___

A 增大

B 减小

C 不变

(6)填空题对于一条逻辑级数可变的逻辑路径,为了减小路径延时,通常将每级门的门努力设为[填空1]

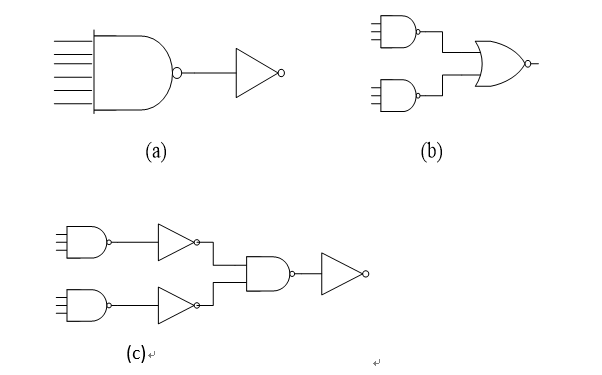

(7)单选题考虑如下3种6输入静态互补CMOS的AND门(标准反相器Wp/Wn=2,自载系数=1)。算一算,当路径电气努力F=1时下列哪个设计最快。( )

A

B

C

获取标准答案请阅读全文

未经允许不得转载!第五节测试 组合逻辑电路的速度优化【含答案】 数字超大规模集成电路设计